실기에서 쓰는 스킬과 관련된 것들: 매 시험마다 1문제씩 나온다고 봐야 하는 것.

(일부?)무료 강의영상: 피쉬본

https://www.youtube.com/watch?v=4vCjYa_gXZ0&list=PLboXycXmAIDt4ObBRPVj29BuD2d27oRnO&index=1

전기회로 관련 자료를 적어두신, 서울사이버대학교 교수님 블로그.

https://blog.naver.com/PostList.naver?blogId=cni1577&from=postList&categoryNo=35

C & I 연구소 : 네이버 블로그

인간의 창의와 기계의 지능에 관해 이야기 나누고 싶습니다. 미래 사회에 관해서도 관심이 많습니다. 또한 일상의 소소한 즐거움에 관해서도 이야기 나누기로 해요.^^ (since 2017. 11. 24.)

blog.naver.com

불 대수: 어지간하면 카르노 맵을 사용

다변수 처리를 수식으로 처리할 줄 아는 사람은 드물고, 기법쓰는것도 빡세니까 카르노 맵 그려다가 푸는게 직관적이고 알기 쉽다.

-불 대수의 연산법칙: 아주 골때리는 스킬이 있는데 접은글에 넣어둔다..

XY'+Y=X+Y

2022년 1회 1번 문제에서 기초법칙 응용으로 최대한 정리해 나온, A'B'D'+AC 를 AC+B'D'로 바꾸는 데 쓴다.

XY'+Y=X+Y 임을 보이는 과정

좌변 =XY'+(X+1)Y = XY'+ XY + Y = X(Y'+Y)+Y =(X×1)+Y=X+Y

-카르노 맵 {공부링크}: 4입력 연산 정리엔 이 카노 맵이 더 좋다.

카르노 맵 작성규칙

- 서로 이어붙는 변수를 적는다.

어지간하면, 변수 2개씩만 붙여서 적는다. 예를 들어서 AB는 되지만 AC는 안된다.

(떨어진 변수끼리 묶어서 적고싶으면 그래라. 그러나 떨어진 변수끼리 모아적은 카르노맵을 풀다간 대가리 빠개지니까 하지말라는 거다.) - 변수 2개씩 이어붙인 것들에서는, 행이나 열 작성해 나갈때 진리값 조정을 1개 변수만 한다.

그래서 통상 00 01 10 11 순으로 표기하는 거랑 다르게, 00 \ 01 \ 11 \ 10 으로 표기한다. - 표의 방향이나 축은 상관없다.

n변수 카르노 맵을 다양하게 그릴 수 있지만, 자신이 자주 쓰는 한가지 유형으로만 그리는 게 좋다.

나는 (행, 열) 순서로 찾는 편이라서 다변수일 때는 2_(A \ B) 3_(A \ BC) 4_(AB \ CD) 등으로 쓴다. 5변수는 (AB \ CDE)로 가끔 쓰는 정도.

아래는, 다양한 형태의 카르노 맵(Karnaugh Map) with 2, 3, 4, 5 변수(variable) 예제(examples)

모두 표시가능한데 종류가 더럽게 많다.

- 번호 붙이는 규칙(numbering)

n변수 카르노 맵에서,

각 변수를 이어붙인 n자리의 이진수 형태를 만든다.

진리값(0,1)을 대입하여 십진수로 환산한다.

더보기예제문제를 보며 이해하기

출력 Y가 입력 A,B,C를 사용하고 Y=Σ(0,2,3,5,6,7)를 만족할 때, (이하생략)

십진수 2 = 이진수 010 이므로, 이는 A' B C' 가 참이다.

십진수 5 = 이진수 101 이므로, 이는 A B' C 가 참이다.

이진논리에서는

{참, High state, 1, True} 등이 다 같은 말이다. 그리고 {거짓, Low state, 0, False} 등도 같은 말이다.

논리 회로: 기본형과 주요 기계

XNOR이랑 Buffer는 거의 안나오니까 잘 몰라도 된다만 알아두면 좋다.

비트 연산자에 쓰는 게이트도 알아야 한다. 관련되어 mask bit 도 나올 수 있다.

| NOT | AND | OR | XOR |

| complement | mask (clear) | Selective-Set | Compare 또는 Selective-Complement

|

| 보수 (반전) | 0으로 만듦 | 1로 만듦 | 비교 또는 선택적 보수 |

반가산기, 반감산기, 전가산기, 전감산기, 병렬가산기, 병렬감산기를 구현하는 논리 회로도. {참고링크}

가감산기 시리즈 기본 4종, 병렬까지 6종은 그림 그대로 외워둔다. (아래 이야기는 기본형태의 조합이다. 게이트 배치는 다양하게 나타날 수 있다.)

| 기본 형태 | 가산기 (adder) | 감산기(subtractor) |

| 반 half | Sum(합) XOR 게이트 Carry(올림수) AND 게이트 |

Difference(차) XOR 게이트 Borrow(빌림수) AND 게이트 NOT 게이트 (X와 D 사이에 둔다.) |

| 전 full | 반가산기 2개 + OR 게이트 | 반감산기 2개 + OR 게이트 |

가산기와 감산기를 '연산 증폭기'(Op Amp)를 사용한 전기회로 구현{그림 암기}: ▷는 버퍼(?)이다. 불대수로는 입력값 = 출력값. (실제로는 전압이 바뀐다.)

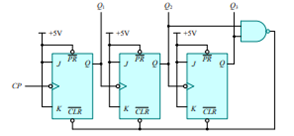

카운터 그림들도 외운다.

카운터: A진 카운터를 만들 때 2^n =< A < 2^(n+1)을 만족하는 n개의 JK-FF 필요하다.

비동기 n진 카운터는 n일때 리셋되도록 설계한다. n_DEC -> n_BIN 으로 바꾼뒤 그 값에 해당하는 위치들의 출력값을 몽땅 가져와 NAND에 연결하고, NAND의 출력을 모든 JK-FF의 clear에 연결한다.

위그림의 예시를 해석하면 비동기 6진이므로 6_DEC -> 110_BIN 따라서 1번(LSB)는 생략하고 2번,3번의 Q를 떼온다.

이론을 현실에 적용하는 것들

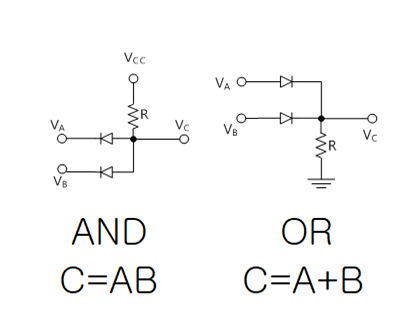

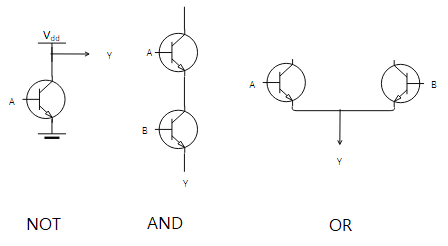

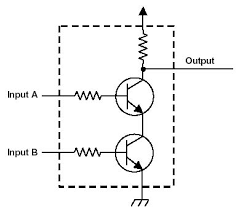

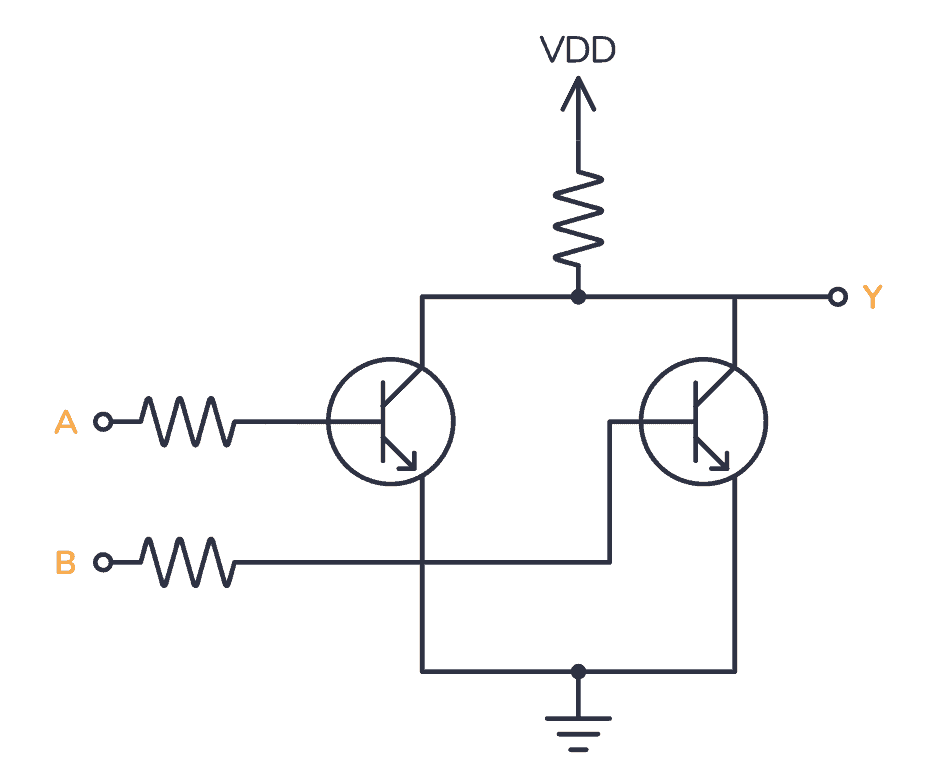

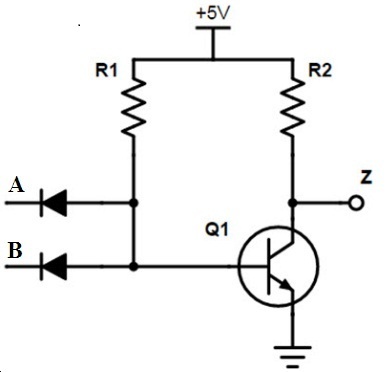

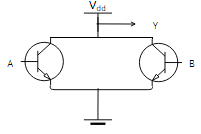

'논리 게이트'를, '전기 회로'로 실제 구현

실제 회로(전원장치, 저항, 다이오드, 트랜지스터)를 이용해서 논리 회로를 구현하는 기술

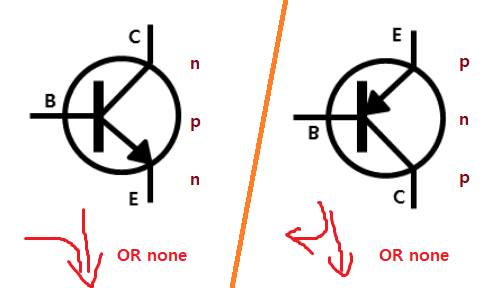

알아야 할 내용: 기초적인 표기법. 다이오드와 트랜지스터의 특성

논리회로의 실제 구현결과물 {링크} 접은글은 내가 보려고 하는용.

그림 위치에 상관없이 회로 구성을 정확히 읽거나 배치할 줄 알아야 한다.

저항은 보통 그려넣는데, 안 그리는 회로들도 있다.

다이오드는 ▷|의 삼각형 끄트머리 방향으로만 전류가 흐른다. 회로가 -▷|- 이면, →는 High(1), ←는 Low(0)이다.

트랜지스터는 마지막 N이 있는 자리에 화살표가 붙는다. 그리고, N방향으로 전류가 모두 흘러들어간다고 생각하면 이해가 쉽다. none으로 설정된 상태는 현실에서는 Z(=high impedence=저항이 엄청 커서 무한대 취급)

(이제 이 두가지 정보를 바탕으로 논리회로의 실제설계를 이해할 수 있다.)

http://gdolicom.blogspot.com/2011/09/bjt-tr-npn-pnp.html

BJT 특성 이해 - 트랜지스터 기본이해 및 해석 - TR NPN. PNP 해석

원문 : BJT 특성 이해 - 트랜지스터 기본이해 및 해석 - TR NPN. PNP 해석 진공관을 사용한 전자 제품 및 컴퓨터를 TR로 대처 함으로써 소형화를 이루는 계기가 되었...

gdolicom.blogspot.com

아래 트랜지스터 회로는 전부 NPN 트랜지스터 썼다.

NAND = NOT(AND), NOR=NOT(OR)이고 첫번째 게이트의 출력을 두번째인 NOT 게이트의 입력으로 주면 구성이 끝난다. 첫번째 게이트는 다이오드회로든, 트랜지스터 회로든 상관없다.

'플립플롭'

플립플롭 = 래치 + 클록

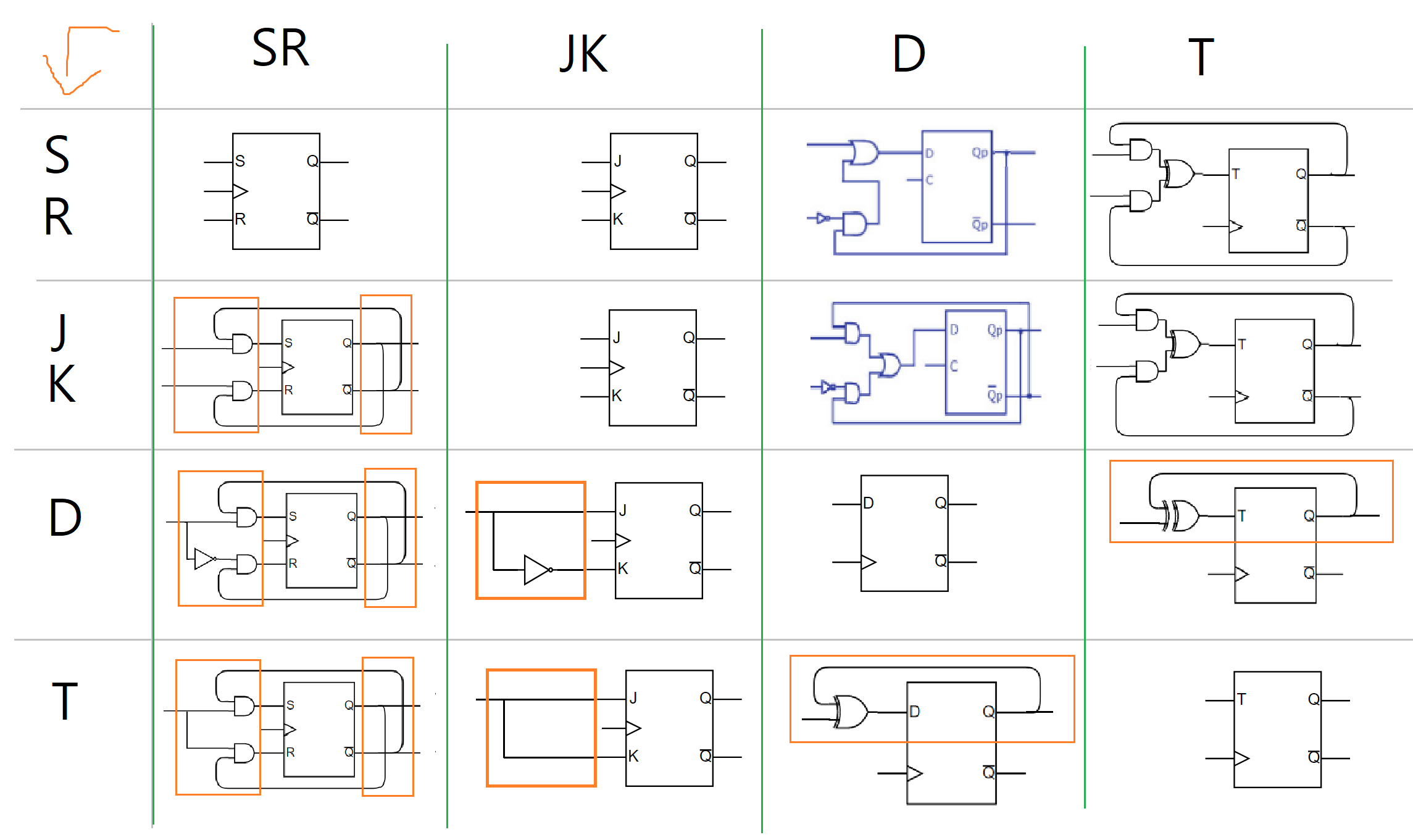

개별 내용은 당연하고, 어떤 플립플롭에 게이트를 추가해서 다른 플립플롭으로 써먹을 수 있는지를 묻는다.

공부하다 왜 얘가 안정된 출력을 내는지 이해안되서 2일 파고들었는데 그런거 할 필요없다. 시험에 필요한 것만 일단 공부해놓고 생각해라.

관련된 내용

'진리표'와 '여기표'도 알아야 한다.

{여기표 변환과정}

플립플롭 변환 (열 to 행)

CPU major state (4개)와 내부의 작동과정, 주요 4연산의 작동과정

{링크의 내용}

Fetch, Indirect, Execute, Interrupt && AND, ADD, LDA, STA

각종 변환

1. 진법 변환

10진(dec), 2진(bin), 8진(oct), 16진(hex) 으로 작성된 수를 같은 값인 다른 진법으로 환산해 작성할 줄 알아야 한다.

구체적인 요령은 구글검색 ㄱㄱ. 시험장에서는 공학용 계산기 쓸 수 있으니 활용한다.

2^n진법끼리 변환은, 소수점 좌우로 n개씩 잘 묶어서 처리한다. 8진법이면 이진수 3개씩, 16진법이면 이진수 4개씩

2. 전/중/후 위식(pre / in / post -fix) 표현 변환 && 순회 방식

- 순회 방식은 전 CLR, 중 LCR, 후 LRC 순서이다. 기본노드 형태로 바꾸어가면서 정리한다.

- 식 표현은 L,R은 피연산자(a,b,c 등 값이 들어가는 자리)이고 C는 연산자(사칙연산 위주) 자리다. 필요한 만큼 잘 괄호 쳐가면서 조금씩 바꿔준다.

수식으로 처리하는 법을 잘 모르겠으면 노드 트리를 그려서 순회로 해석하고.

(각종 공식을 사용해) 계산하는 문제

0. 메모리 계산 및 관련 크기

제일 까다롭다고 생각드는 문제들. 비슷해서 많이 헷갈린다.

기억장치의 용량 = 2^a × b 에서

a =워드의 수 =MAR 비트수 =PC 비트수 = 입력번지선(주소선)의 수

b =워드의 크기 =MBR 비트수 = IR 비트수 = AC 비트수 = 출력데이터선의 수 = 데이터 버스의 비트수

※ AC는 데이터 임시 저장하는 공간이므로, 워드의 크기와 같다.

1. 클록

좀 까다로운 문제가 클록 주기(단위 sec)와 클록 주파수(단위 Hz == 1/s) 계산

주기×주파수 = T×f = 1 하나만 알고 가도 역산에 큰 어려움은 없다.

(주로) 10^(3z) 단위로 나오는 각종 접두어 영단어도 암기.

2. 주소 계산방식 종류와, 실제로 계산하기

직접, 간접, 절대, 상대 등등

상대주소 계산시 fetch 단계에서 PC <- PC+1 되는 상황이면 주소값 계산할때 1 더해 주어야 한다.

3. 프레임 계산 / 디스크 총 접근시간 계산

FIFO / FCFS 등으로 물어본다.

- 계산공식 HRN 우선순위 값 = (대기시간+수행시간) / 수행시간

4. 정렬 / 탐색: 최악, 표준, 최적 시간대도 같이 암기

개정 이후 C언어로 이 정렬이나 탐색 기법 물어보는 문제가 나온다. 대체로 최종값을 계산하는 코딩문제.

5. 이진수와 그레이코드 바꾸기

MSB는 그대로 가져간다.

- Bin to Gray : 2진수 두개(n번째, n+1번째)의 비트를 XOR 하여 n+1번째 비트로 설정. 일명 yyyy

- Gray to Bin : Gray(n번째)와 2진수(n+1번째)의 비트를 XOR 하여 n+1번째 비트로 설정. 일명 nnnn

6. 해밍코드 변환 (대체로 짝수 패리티로 제공)

- 패리티 비트 자리부터 만들어 놓고, 데이터 채운다.

- 패리티 비트 맞춘다.

7. 적중률과 실패율(미스율)

적중률 = 원하는 데이터가 캐시에 있는 횟수 / 전체 기억장치 액세스 횟수

미스율 = 1 – 적중률

기타 고빈출 암기문제: 단어와 설명 같이 외우시오.

- 어셈블리 지시어 = 의사 명령(psuedo instruction): 어셈블러가 어셈블러에 필요한 작업을 지시하는 명령. 기계어 번역x

- 비동기식 제어신호 교환: Handshaking 과 Strobe pulse (핸드세이킹, 스트로브펄스)

- Burst 와 Cycle stealing (버스트, 사이클 스틸링)

- 제어장치: Hard-wired 와 Micro-programming (고정배선 제어장치, 마이크로 프로그래밍)

- 0~3주소 명령어

- n비트 병렬가산기에서 오버플로 회로 그리기: MSB와 그다음 비트를 입력받아 XOR 연산

- 메모리 적합: first, best, worst

- BCD 가산기 회로 빈칸: 그림 암기

- Polling 과 Daisy-chain (소프트웨어 1종 폴링 / 하드웨어 3종 직렬_데이지체인, 병렬, 벡터? )

- RISC 와 CISC (Reduced/Complex Instruction Set Computer): RISC에 Load, Store, 계산형 명령어(레지스터3개참조)

- DMA: 입출력장치가 CPU를 경유하지 않고 주기억장치에 데이터를 전송하는 방식

- 버스 종류: Address, Data, Control

- 내부/외부 인터럽트

- Loader의 4가지 기능: Allocation, Relocation, Loading, Linking (할당, 재배치, 적재, 연결)

- Absolute Loader에서는 Allocation은 프로그래머가, Relocation은 어셈블러가 담당.

- Micro Operation: 명령을 수행하기 위해 CPU내의 레지스터와 플래그의 상태 변환을 일으키는 작업

- RAID: 0(연장), 1(복제), 5(패리티 분산저장) 과 이를 결합하여 쓰는 정도

- 플린의 컴퓨터 구조: SISD, SIMD, MISD, MIMI 4종류. single/multiple * instruction/datastream

- 스레싱(thrashing): 페이지 교체 시간 > 프로세스 처리시간

- OS의 시스템소프트웨어는6종류: 제어프로그램 3개(감시프로그램, 작업관리(=스케줄러)프로그램, 자료관리프로그램) && 처리프로그램3개(언어번역기, 서비스프로그램, 문제처리프로그램)

- 유닉스(unix): shell, kernerl (쉘, 커널)

- CPU의 관여 정도: Programmed I/O && Interrupted I/O && DMA

- 메모리: memory-mapped I/O (같은 명령어, 기억공간 사용) && isolated I/O (다른 곳 사용)

- crosstalk 인접 신호선 사이의 잡읍

- pheripheral register 데이터를 주변장치로 전달시 사용

- trunaround time

레지스터 기본 종류

- Accumulator ALU 보조 레지스터로서 계산결과가 일시적 저장

- Program Counter 다음에 수행할 명령의 주소 저장

- Stack Pointer 서브루틴 호출이나 인자전달 등에 사용된다

- Base Register 기준주소지정에 사용되는 레지스터로, 이 레지스터 값과 명령에 지정된 offset으로부터 유효주소가 만들어진다

- Flag Register CPU의 산술 논리 연산의 결과로 캐리부호, 오버플로우 등의 상태를 저장

- Index Register 색인주소지정에 사용되는 레지스터로, 기준주소와 인덱스 레지스터에 둔 값이 합쳐서 유효주소를 만들어낸다.

- Instruction Register 현재 수행 중인 명령어 코드 저장

노드 관련 용어

| 용어 | 의미 |

| 노드(Node) | 정보 항목 |

| 근(root) 노드 | 최상위 노드 |

| 부모(parent) 노드 | 기본트리에서 상위레벨에 있는 노드 |

| 자식(child) 노드 | 기본트리에서 하위레벨에 있는 노드 |

| 형제(siblings) 노드 | 부모 노드가 같은 자식 노드들 |

| 조상(ancestor) 노드 | 어떤 노드에서 루트에 이르는 경로에 해당하는 모든 노드. |

| 후손(descendant) 노드 | 어떤 노드의 하위 노드에 있는 모든 노드 |

| 단말(terminal) 노드 | 자식이 없는 노드 |

| 에지(edge) | 노드 사이의 연결 (일명 선) |

| 레벨(level) | 루트의 레벨을 0로 정의하고, 아래로 1을 더해 나감. |

| 노드 차수(degree) | 자식 노드의 수 |

| 깊이(depth), 높이(height) | 트리의 최대 레벨 |

교착 상태

| 발생 조건 4 | 해법 4 |

| 상호배제(Mutual Exclusion) 점유 및 대기(Hold and Wait) 비선점(Non-Preemption) 환형 대기(Circular Wait) |

예방(prevent) 회피(avoid) 탐지(detect) 무시 (ignore) |

출처와 참고자료

'자격증 > 전자계산기 (조직응용)기사' 카테고리의 다른 글

| 2023년 1회, 3회 전자계산기 조직응용기사 실기 후기 (4) | 2023.04.23 |

|---|---|

| 전자계산기 조직응용기사: 실기 필답형 기출 복원문제 해설집 (1) | 2023.04.21 |

| 전자계산기 조직응용기사 필기 요약집 pdf (v23.03) (1) | 2023.03.28 |

| 전자계산기 조직응용기사 실기(필답형) 기출문제 목록 얻는곳 (1) | 2023.03.28 |

| 3단원 전자계산기구조] 불 대수(=논리연산) 쉽게 생각하기 (0) | 2023.03.15 |